- 您現在的位置:買賣IC網 > PDF目錄22131 > ATF1502BE-7AU44 (Atmel)IC CPLD EE HP 7NS 44TQFP PDF資料下載

參數資料

| 型號: | ATF1502BE-7AU44 |

| 廠商: | Atmel |

| 文件頁數: | 24/24頁 |

| 文件大小: | 0K |

| 描述: | IC CPLD EE HP 7NS 44TQFP |

| 標準包裝: | 160 |

| 系列: | ATF15xx |

| 可編程類型: | 系統內可編程(最少 10,000 次編程/擦除循環) |

| 最大延遲時間 tpd(1): | 7.5ns |

| 電壓電源 - 內部: | 1.7 V ~ 1.9 V |

| 宏單元數: | 32 |

| 輸入/輸出數: | 32 |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 44-TQFP |

| 供應商設備封裝: | 44-TQFP(10x10) |

| 包裝: | 托盤 |

| 配用: | ATF15XX-DK3-ND - KIT DEV FOR ATF15XX CPLD'S |

9

3492A–PLD–12/05

ATF1502BE

5.2

On-the-Fly – OTF

In this mode, the CPLD design pattern stored in the internal configuration memory can be modi-

fied while the previous design pattern is operating with minimal disturbance to the operation of

the current design. The new configuration will take affect after the OTF programming process is

completed and the OTF mode is exited.

The configuration data for any design is stored in the internal configuration memory. Once the

configuration data is transferred to the internal static registers of the CPLD, the CPLD operates

with the design pattern and the configuration memory is free to be re-loaded with a new set of

configuration data. The design pattern due to the new configuration content is activated through

an initialization cycle that occurs on exiting the OTF mode or after the next power up sequence.

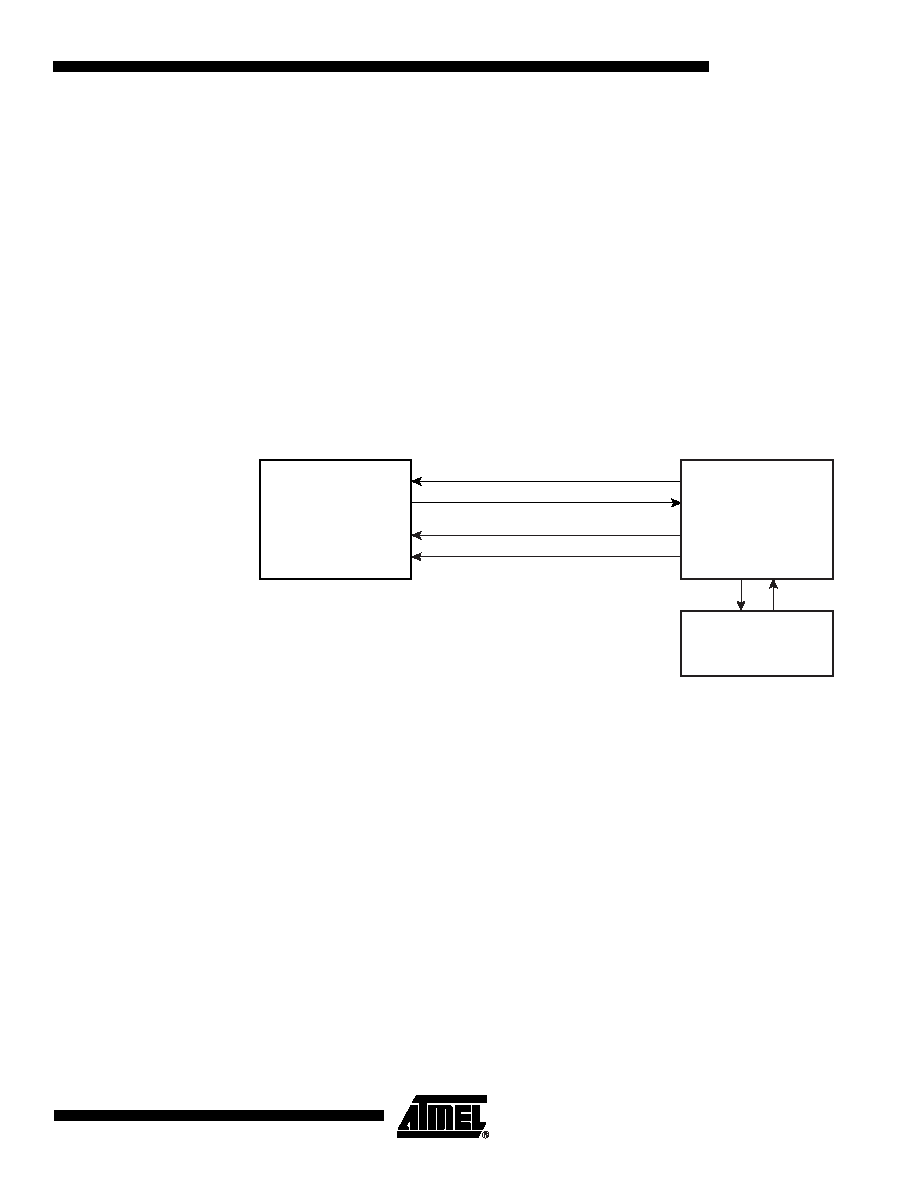

Figure 5-2 shows the electrical interface for configuration of the ATF1502BE device in the OTF

mode. The processor is the controlling device that communicates with the CPLD and uses con-

figuration data stored in the external memory to configure the CPLD.

Figure 5-2.

Configuration of ATF1502BE Device Using a Processor and Memory

5.3

Direct Reconfiguration Access – DRA

This reconfiguration mode allows the user to directly modify the internal static registers of the

CPLD without affecting the configuration data stored in the embedded memory. It is more useful

in cases where immediate and temporary context change in the function of the hardware is

desired.

The CPLD embedded configuration memory does not change when a new set of configuration

data is passed to the chip using the DRA mode. Instead, the internal static registers of the CPLD

are directly written with the data entering the chip via the JTAG port. In other words, it's a tempo-

rary change in the function performed by the CPLD since a power sequence results in the device

being configured again by the data stored in the embedded memory.

5.4

ISP Programming Protection

The ATF1502BE has a special feature that locks the device and prevents the inputs and I/O

from driving if the programming process is interrupted for any reason. The inputs and I/O default

to high-Z state during such a condition.

TCK

ATF1502BE

CPLD Device

Processor

Memory

Address

Data

Serial Data

TDI

TMS

TDO

相關PDF資料 |

PDF描述 |

|---|---|

| B340B-13-F | DIODE SCHOTTKY 40V 3A SMB |

| RSM30DTAT-S189 | CONN EDGECARD 60POS R/A .156 SLD |

| RBA14DTKH | CONN EDGECARD 28POS DIP .125 SLD |

| RMM30DTAT-S189 | CONN EDGECARD 60POS R/A .156 SLD |

| RGM30DTAT-S189 | CONN EDGECARD 60POS R/A .156 SLD |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ATF1502SE | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Family Datasheet |

| ATF1502SE(L) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATF1502/04/08/16SE(L) Preliminary [Updated 9/02. 69 Pages] Second Generation Industry Compatible 5V Logic Doubling CPLDs 32-512 Macrocells. standard & low power w/ISP |

| ATF1502SE-10 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Family Datasheet |

| ATF1502SE-5 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Family Datasheet |

| ATF1502SE-6 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Family Datasheet |

發布緊急采購,3分鐘左右您將得到回復。